[Pwr], so they will not be repeated here.- Quick menu:

- pwr.sub:

- 3lvl_mod

- 3ph_ACMotor

- 3ph_br_cm, 3ph_br_vm

- 3ph_gen

- 3ph_LC

- 3ph_snub

- 3ph_SW

- BrdgRect

- BrdgRectThy

- Cable

- DC_trafo

- Disturb

- HystComp

- Isense

- RLC

- SVHCC

- SVPWM

- UcD_block

- Vsense

- Wattmeter

- wt

- sym.sub:

- sym

- transforms.sub:

- Transforms

- Downloads

Subcircuits in pwr.sub:

3lvl_mod

Three-phase, three level modulation, with external carrier, but not restricted to 3-phase applications.

|

|

||||||||||||||||||||||||

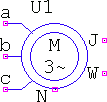

3ph_ACMotor

A three-phase AC motor model.

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

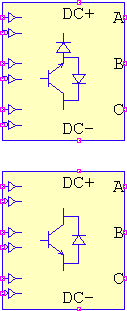

3ph_br_cm, 3ph_br_vm

Three-phase switching bridges, current-mode and voltage-mode, not restricted to 3-phase applications.

|

|

||||||||||||||||||||||||

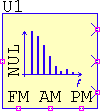

3ph_gen

Three-phase voltage or current harmonics generator.

The harmonics are generated based on these formulas:

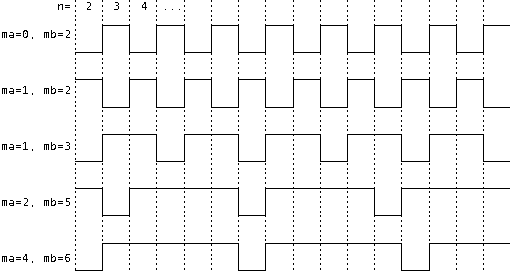

sn sets the signum on a cycle basis, where mb determines the period, and ma the offset. Setting both to zero disables the whole signum function. Non-integer values also work. The fundamental is not affected. Here are the outputs, from the 2nd harmonic up, for various settings (low means -1 and high means 1): And here are a few predefined settings to achieve some commonly found waveforms ("~" means "don't care", and "#" means the ones listed below are for ma=0, mb=0, but variations are possible for mb>1):

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

3ph_LC

Three-phase LC lowpass, delta or wye for capacitors.

|

|

||||||||||||||||||

3ph_snub

Three-phase series RC snubber, delta or wye.

|

|

|||||||||||||||

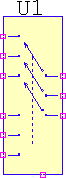

3ph_SW

Three-phase to three-phase externally controlled timed switch, or glorified multiplexer.

|

|

||||||||||||||||||

BrdgRect

Three-phase bridge rectifier, but not restricted to 3-phase applications.

|

|

|||||||||||||||||||||||||||

BrdgRectThy

Three-phase thyristor rectifier with external control.

|

|

||||||||||||||||||||||||||||||||||||||||||

Cable

A three-phase power cable model.

|

|

||||||||||||||||||||||||||||||||||||

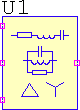

DC_trafo

Small signal DC trafo with external duty cycle control.

|

|

|||||||||||||||

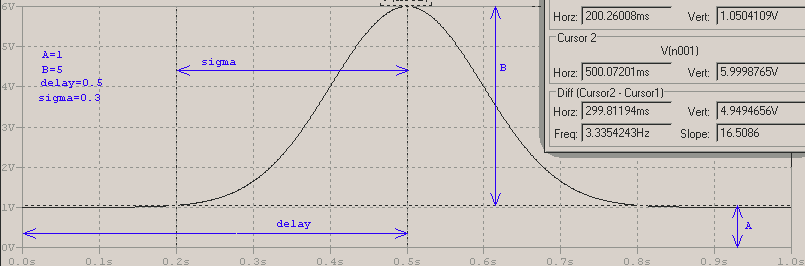

Disturb

Disturbance inducer.

|

|||||||||||||||||||||||||||||||

HystComp

Hysteresis comparator with external enable and error band, and complementary outputs.

|

|

|||||||||||||||||||||

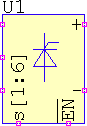

Isense

Isolated current sensor.

|

|||||||||||||

RLC

Universal three-phase RLC load: wye (with or without null) or delta, series or parallel, with any power combinations possible.

|

|

||||||||||||||||||||||||||||||

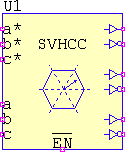

SVHCC

Space-vector hysteresis current controller, 3-phase only.

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

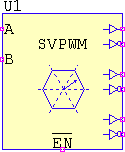

SVPWM

Space-vector PWM controller, quadrature input (sin/-cos), three-phase applications, only.

|

|

||||||||||||||||||||||||||||||

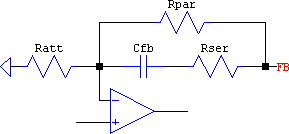

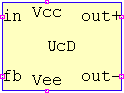

UcD_block

Full-bridge, non-inverting UcD amplifier, inspired by Bruno Putzeys↗.

|

|

||||||||||||||||||||||||||||||

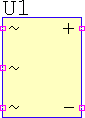

Vsense

Isolated voltage sensor.

|

|

||||||||||||

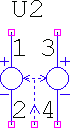

Wattmeter

Wattmeter, single phase, the current flow is indicated by the arrow.

[note] About limsh and corr:

SAMPLEHOLDs are A-devices, so they have vhigh and vlow as parameters, and when the output reaches those limits, the s&h doesn't simply limit the output, but cuts its amplification by a factor of 1000. This is due to the default rclamp=1, while rout=1k. This can be tested this with the following setup:

Vin in 0 pwl 0 0 1 1k ; ramp input Vin feeds a ramp from 0 to 1k for 1s, Vsh forces the s&h to act as a repeater, and Atest has set vhigh=1. The output will be ~2V@1s (rout||rclamp). On the other hand, if you want to set the limits high, it seems that 1e18 is about the limit, because at 1e19 and up glitches happen. So, for this case in particular, if the internal limits (the squaring of powers) tend to reach 1T, or higher, a safer way to deal with the limitation is to set vhigh for the s&h to be very low, so that the 1000x attenuation is in effect early on, and simply amplify it afterwards. Precision will be affected, most likely (at these powers it shouldn't matter that much), but the limits now can be higher than 1e18, which, as high as this value already is, they can be reached when the wattemeter is used for tens or hundreds of kV and kA. Therefore, by default, limsh==lim, unless lim>1G, when it is 1m, while the correction factor corr=1 for lim<1G, else corr=1k. |

|||||||||||||||||||||||||

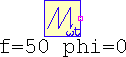

wt

Angle generator.

|

|

|||||||||||||||

Subcircuits in sym.sub:

abc-120, 120-abc

Symmetrical components analyzer.

|

|

||||||||||||||||||||||||

Subcircuits in transforms.sub:

abc/AB0, AB0/abc, abc/dq0, dq0/abc, AB/dq, dq/AB, abc/120, 120/abc

Three-phase transformations: stationary frame, rotating, and symmetrical components, a quasi-instantaneous approach.

|

|

||||||

- Pwr.zip (38987 B)

- MD5=dc4d2e18b6482d8817761a9e34c7b388

- SHA256=5cc8808323220497873ba001534a05fe4db4a996d1efec1c02ae9402f2a3e97d